ปัจจุบันนี้เทคโนโลยี CPU, Memory และ Storage ก็ก้าวหน้าขึ้นไปทุกวัน ความเร็วของแต่ละระบบนั้นสูงขึ้นเรื่อยๆ จน Bus นั้นเริ่มกลายเป็นคอขวดของระบบ ทำให้เหล่าผู้ผลิตชั้นนำทั่วโลกต้องมาร่วมมือกันภายใต้กลุ่ม Gen-Z Consortium เพื่อร่วมกันออกแบบสถาปัตยกรรม Memory Bus ใหม่ด้วยกัน โดยมุ่งเน้นที่ความสามารถดังต่อไปนี้

- เพิ่ม Bandwidth และลด Latency ลง โดยจะมี Bandwidth สูงตั้งแต่หลายสิบ GB/s ไปจนถึงหลายร้อย GB/s และมี Latency ต่ำกว่า 100ns

- รองรับการเพิ่ม Memory ในระบบได้แบบ Real-time เพื่อตอบโจทย์การเพิ่มขยายทรัพยากรในระบบได้โดยไม่มี Downtime

- สามารถทำการกับระบบปฏิบัติการที่มีอยู่เดิมได้โดยไม่ต้องปรับแต่งและแก้ไขอะไร และรองรับการขยายได้ตั้งแต่ระดับเครื่องไปจนถึงระดับ Rack

- เป็นมาตรฐานกลางแบบเปิด สำหรับให้ทุกคนในอุตสาหกรรมนำไปใช้ได้

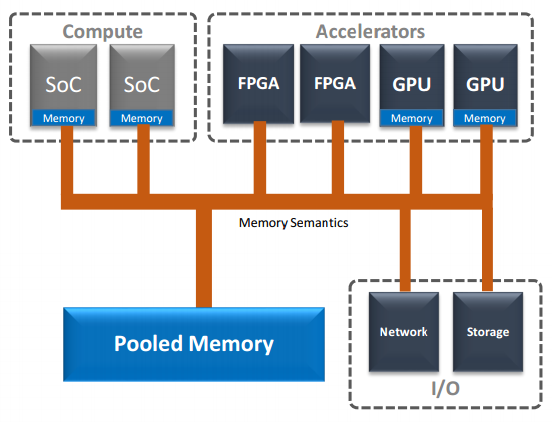

ในโครงการนี้ยังได้มีการนำเสนอแนวคิด Memory Semantic Fabric ที่จะทำให้ CPU สามารถเข้าถึงข้อมูลต่างๆ ได้ด้วย Memory Operation อย่าง Load/Store, Put/Get และ Atomic Operation ต่างๆ ได้โดยตรง ซึ่งจะทำให้การเข้าถึงข้อมูลต่างๆ มีความง่ายกว่าเดิมเป็นอย่างมาก เพราะเดิมการเข้าถึงข้อมูลในระบบ Storage นั้นจะเป็นแบบ Block-based ที่ต้องมีชั้นของ Software มาจัดการโดยเฉพาะ แนวคิดนี้จะช่วยให้การเข้าถึงข้อมูลกลุ่ม Storage Class Memory (SCM) หรือการเข้าถึงข้อมูลจาก Pool ต่างๆ ในระดับ Rack Scale และการเข้าถึงข้อมูลภายในระบบแบบ Multi-node มีความซับซ้อนน้อยลง แต่มีความเร็วสูงขึ้น

ปัจจุบัน Gen-Z Consortium มีสมาชิกได้แก่ AMD, ARM, Cavium Inc., Cray, Dell EMC, Hewlett Packard Enterprise (HPE), Huawei, IBM, IDT, Lenovo, Mellanox Technologies, Micron, Microsemi, Red Hat, Samsung, Seagate, SK hynix, Western Digital Corporation และ Xilinx

ผู้ที่สนใจสามารถศึกษาข้อมูลเพิ่มเติมได้ที่ http://genzconsortium.org/ และ http://genzconsortium.org/wp-content/uploads/2016/05/Gen-Z-Consortium-Briefing-Deck_Final.pdf ได้ทันทีเลยนะครับ

TechTalkThai ศูนย์รวมข่าว Enterprise IT ออนไลน์แห่งแรกในประเทศไทย

TechTalkThai ศูนย์รวมข่าว Enterprise IT ออนไลน์แห่งแรกในประเทศไทย